Rambus schlägt Techniken für kommende PC-Hauptspeichergenerationen vor

Mit zahlreichen Vorschlägen für Innovationen bringt sich Rambus als Technik-Zulieferer für kommende DRAM-Generationen ins Spiel.

(Bild: Rambus)

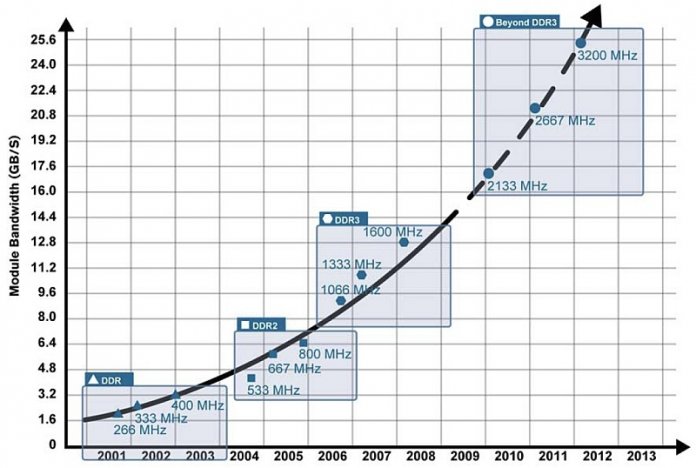

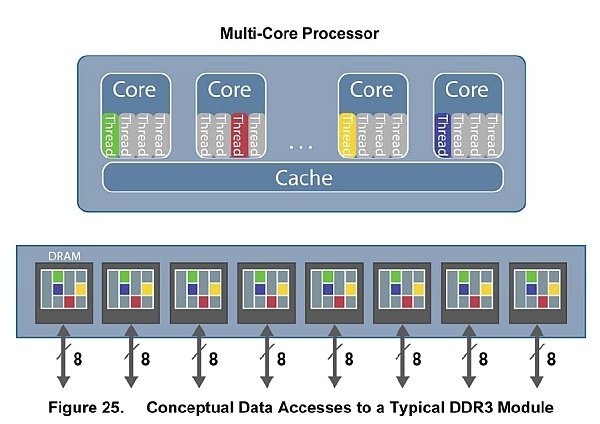

Die kalifornische Entwicklerfirma Rambus [1] stellt in einem 34-seitigen White Paper [2] (PDF-Datei) zahlreiche neue Techniken für kommende Hauptspeicher [3]-Generationen "nach DDR3" – also beispielsweise DDR4 [4]. Darin spricht das außer für seine zahlreichen juristischen Auseinandersetzungen [5] und für RDRAM- und XDR [6]-Speicher bekannte Unternehmen, das aber etwa auch DDR2-SDRAM [7]-Controller und PCI-Express-Funktionsblöcke [8] entwickelt, viele offene Probleme an. So zeigt Rambus beispielsweise, wie sich der Energiebedarf von DRAM [9]-Interfaces bei steigender Datentransferrate im Zaum halten lässt. Auch die (nicht ganz neuen) Ansätze zum "Threading [10]" von RAM-Zugriffen, die speziell in Multi-Core-Systemen hilfreich sein können, sind interessant.

(Bild: Rambus)

Schließlich diskutiert das Papier das Problem, dass sehr hohe Datentransferraten mit der aktuellen Technik von ungepufferten und Registered-DIMMs nur bei kleinem Hauptspeicherausbau erreichbar sind, dass also mit wachsender RAM-Bestückung die Taktfrequenz des Speicherbusses sinkt. Die von Intel federführend [11] als Lösung dieses Problems entwickelte Fully-Buffered-(FB-)DIMM-Technik hatte sich als wenig [12] energieeffizient entpuppt und kommt bald nur noch in High-End-Servern zum Einsatz. Konkret schlägt Rambus außer Threading beispielsweise ein Signalisierungsverfahren mit extrem geringen Spannungspegeln vor (Near Ground Signaling) sowie eine spezielle Verteilung der Taktsignale (FlexClocking [13]). Zudem könnten Speicherchips künftig schneller zwischen Stromspar- und Betriebsmodi umschalten. (ciw [14])

URL dieses Artikels:

https://www.heise.de/-220267

Links in diesem Artikel:

[1] http://www.rambus.com/

[2] http://www.rambus.com/assets/documents/products/future_main_memory_whitepaper.pdf

[3] https://www.heise.de/news/Rambus-will-zurueck-auf-den-PC-Hauptspeicher-Markt-159172.html

[4] https://www.heise.de/news/IDF-Nach-DDR3-kommt-DDR4-Hauptspeicher-197943.html

[5] https://www.heise.de/news/Rambus-gewinnt-Berufungsverfahren-gegen-US-Wettbewerbshueter-202222.html

[6] https://www.heise.de/news/Rambus-Speichertechnik-XDR2-soll-2007-kommen-114220.html

[7] http://www.heise.de/glossar/entry/Synchronous-Dynamic-RAM-398557.html

[8] https://www.heise.de/news/IDF-Rambus-Technik-im-ULi-Chipsatz-und-anderswo-125352.html

[9] http://www.heise.de/glossar/entry/Dynamic-Random-Access-Memory-395584.html

[10] https://www.heise.de/news/Rambus-entwickelt-Micro-Threading-fuer-DRAM-Speicherchips-150100.html

[11] https://www.heise.de/news/Neue-Speichertechnik-rueckt-naeher-104635.html

[12] https://www.heise.de/news/Studie-Opteron-Server-effizienter-als-Xeons-mit-Fully-Buffered-DIMMs-178740.html

[13] http://www.rambus.com/de/patents/innovations/detail/flexclocking.html

[14] mailto:ciw@ct.de

Copyright © 2009 Heise Medien