Linux auf einem OpenPOWER-System installieren

Farbenwechsel

POWER-Prozessoren spielen ihre Vorteile vor allem bei Virtualisierung und Datenbankanwendungen aus. Auf dieser Architektur lässt sich nahezu uneingeschränkt Linux benutzen – und die quelloffene BIOS-Firmware bietet viele Vorteile.

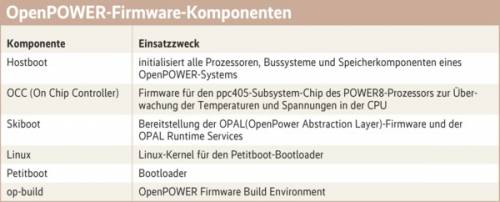

Linux-Distributionen haben als Serverbetriebssystem einen festen Platz in heutigen Rechenzentren. Dass der Linux-Kernel darüber hinaus viele weitere Anwendungsszenarien besitzt, bezeugen neben Android-Smartphones und Raspberry Pis auch OpenPOWER-Systeme. Dort kommt der Kernel bereits bei der Firmware zum Einsatz. Statt ein proprietäres BIOS- oder UEFI-Firmware-Image verwenden zu müssen, kann man seine Firmware selbst kompilieren. Von der ersten Instruktion zur Hardware-Initialisierung des ersten Prozessor-Cores über das Betriebssystem bis hin zur Datenbank führt ein POWER-Server ausschließlich Open-Source-Code aus. Der Artikel zeigt, wie man dabei vorgeht.

Im August 2013 hatte IBM gemeinsam mit Google, Mellanox, NVIDIA und Tyan ein OpenPOWER-Konsortium (openpowerfoundation.org, siehe auch „Alle Links“ am Artikelende) als Bündnis zur offenen Entwicklung von Serversystemen basierend auf IBMs POWER-CPUs angekündigt. Ein Jahr später veröffentlichte IBM den ersten Open-Source-Firmwarecode für POWER8-Systeme auf GitHub. Seither wird dort die Firmware von Mitgliedern der OpenPOWER-Foundation und weiteren Entwicklern gepflegt.

Offene Firmware und Industriebündnis

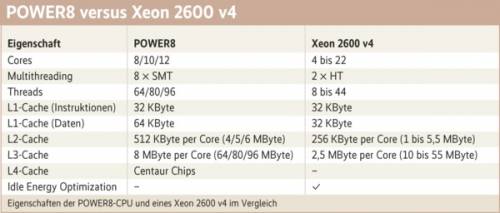

In OpenPOWER-Servern kommen derzeit IBMs POWER8-CPUs zum Einsatz, die sich in mehreren Punkten von x86-Server-CPUs unterscheiden: Sie haben typischerweise 8, 10 oder 12 Cores pro Prozessor. Mittels Simultaneous Multi-Threading (SMT) – einer Funktion ähnlich dem Hyperthreading von Intel-CPUs – kann jeder Core1, 2, 4 oder 8 Threads parallel verarbeiten (SMT-1 bis SMT-8). Jeder Core hat dabei dedizierte Ressourcen für vier Threads. Eine einzelne POWER8-CPU bietet damit bis zu 96 parallele Threads.

Darüber hinaus haben POWER-CPUs besonders große Caches: 512 KByte L2-Cache werden von 8 MByte L3-Cache (je Core) ergänzt. Ein weiterer Cache-Level (L4) befindet sich in den sogenannten Centaur Memory Buffers, die unterschiedliche Arbeitsspeichertypen anbinden. Mit diesen groß dimensionierten Caches will IBM vor allem Datenbankanwendungen beschleunigen, weil beim Einsatz dieser Applikationen seltener auf den langsameren Arbeitsspeicher zugegriffen werden muss.

Im Gegensatz zu den früheren POWER-CPUs arbeitet die achte Prozessorgeneration auch mit der Little-Endian-Byte-Reihenfolge; bis POWER7 setzte IBM auf Big Endian. Vor allem um die Portierbarkeit von Anwendungen aus anderen Architekturen wie x64_64 zu vereinfachen, entwickelte IBM POWER8 mit beiden Byte-Reihenfolgen; im Bereich von OpenPOWER kommt Little Endian zum Einsatz. Big Endian hat nur noch auf POWER8-Systemen von IBM Bedeutung, die mit IBMs Unix-Variante AIX oder – meist per Logical Partition (LPAR) virtualisierten – Linux-Systemen laufen.

Server für POWER8-CPUs können seit Gründung der OpenPOWER-Foundation auch von anderen Herstellern als IBM angeboten werden. Gefertigt werden solche beispielsweise von Tyan oder Wistron (siehe iX-Artikel „Offener Angriff“ [1] über ein Tyan-Referenzsystem).

Transparenter Bootprozess

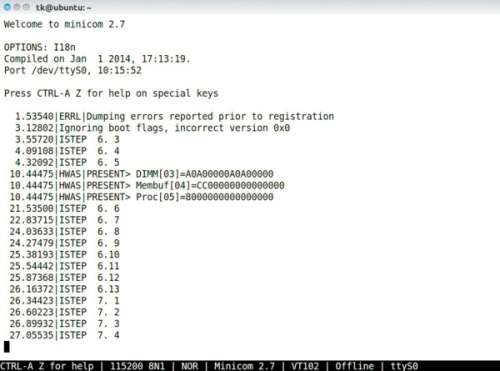

Die OpenPOWER-Firmware besteht aus mehreren Komponenten, die nacheinander zur Initialisierung des Servers ausgeführt werden. Die 21 Schritte heißen ISTEPs (Initialization Steps) und sind durchnummeriert. Beim Serverstart erscheinen auf der seriellen Konsole detaillierte Informationen zu den derzeit durchgeführten Schritten (Abbildung 1). Das erleichtert bei Bootproblemen die Analyse erheblich – so lassen sich auf diese Art etwa falsche RAM-Belegungen erkennen. Zu Beginn (ISTEPS 1 bis 4) initialisiert die Self Boot Engine die CPU und startet anschließend die nächste Komponente (Hostboot). Diese initialisiert in den ISTEPS 5 bis 21 alle weiteren Komponenten (CPU-Bus, Memory-Subsystem, CPU-Cores).